- 您现在的位置:买卖IC网 > Sheet目录2011 > MAX5893EGK+D (Maxim Integrated Products)IC DAC 12BIT DUAL 500MSPS 68-QFN

MAX5893

12-Bit, 500Msps Interpolating and Modulating

Dual DAC with CMOS Inputs

______________________________________________________________________________________

11

Pin Description (continued)

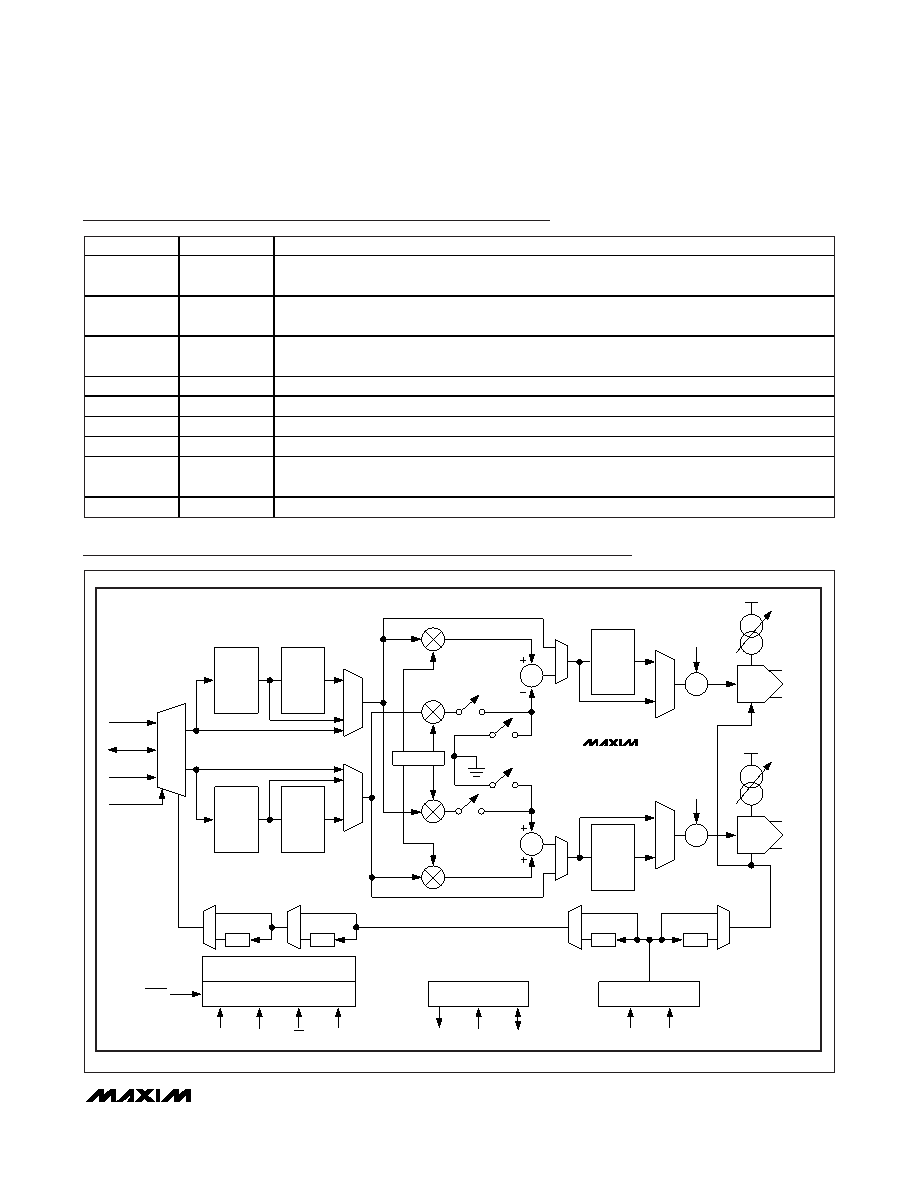

Functional Diagram

PIN

NAME

FUNCTION

53, 67

AVDD1.8

Low Analog Power Supply. Accepts a 1.71V to 1.89V supply range. Bypass each pin to GND with

a 0.1F capacitor as close to the pin as possible.

54, 56, 59, 61,

64, 66

GND

Ground

55, 60, 65

AVDD3.3

Analog Power Supply. Accepts a 3.135V to 3.465V supply range. Bypass each pin to GND with a

0.1F capacitor as close to the pin as possible.

57

OUTQN

Inverting Differential DAC Current Output for Q-Channel

58

OUTQP

Noninverting Differential DAC Current Output for Q-Channel

62

OUTIN

Inverting Differential DAC Current Output for I-Channel

63

OUTIP

Noninverting Differential DAC Current Output for I-Channel

68

AVCLK

Clock Power Supply. Accepts a 3.135V to 3.465V supply range. Bypass to ground with a 0.1F

capacitor as close to the pin as possible.

—

EP

Exposed Pad. Must be connected to GND through a low-impedance path.

IDAC

OUTIP

OUTIN

QDAC

OUTQP

OUTQN

SELIQ

A0–A11

B0–B11

DATACLK

SERIAL INTERFACE

CONTROL REGISTERS

REFERENCE

MODULATOR

CLOCK BUFFERS

AND DIVIDERS

CLKP

CLKN

RESET

fCLK

fDAC

DA

TA

SYNCH

AND

DEMUX

MUX

Q

I

Q

I

2x

INTERPOLA

TING

FIL

TER

2x

INTERPOLA

TING

FIL

TER

2x

INTERPOLA

TING

FIL

TER

2x

INTERPOLA

TING

FIL

TER

2x

INTERPOLA

TING

FIL

TER

2x

INTERPOLA

TING

FIL

TER

MUX

DIGITAL

OFFSET

ADJUST

DIGITAL

OFFSET

ADJUST

DIGITAL

GAIN

ADJUST

/2

SDO

SDI

CS

SCLK

DACREF

FSADJ

REFIO

∑

fIM/2, fIM/4

∑

DIGITAL

GAIN

ADJUST

/2

MAX5893

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MAX5894EGK+D

IC DAC 14BIT DUAL 500MSPS 68-QFN

MAX5895EGK+D

IC DAC 16BIT 500MSPS DUAL 68-QFN

MAX5898EGK+D

IC DAC 16BIT DUAL 500MSPS 68-QFN

MAX6900ETT+T

IC RTC I2C COMPAT 6-TDFN

MAX6902ETA+T

IC RTC SPI COMPAT 8-TDFN

MAX7375AXR604+T

IC OSC SILICON SC70-3

MAX7394ATTLY+T

IC OSC SILICON 922KHZ 6-TDFN

MAX7403CSA+

IC FILTER LOWPASS 8-SOIC

相关代理商/技术参数

MAX5893EGK+TD

功能描述:数模转换器- DAC 12-Bit 2Ch 500Msps DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX5893EGK-D

功能描述:数模转换器- DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX5893EGK-TD

功能描述:数模转换器- DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX5893EVCMOD2

功能描述:数模转换器- DAC Evaluation Kit for the MAX5893/MAX5894/MAX5895 RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX5893EVKIT

功能描述:数模转换器- DAC Evaluation Kit for the MAX5893/MAX5894/MAX5895 RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX5894EGK+D

功能描述:数模转换器- DAC 14-Bit 2Ch 500Msps DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX5894EGK+TD

功能描述:数模转换器- DAC 14-Bit 2Ch 500Msps DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX5894EGK-D

功能描述:数模转换器- DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube